1.本发明涉及一种栅极驱动装置及显示面板。

背景技术:

2.近年来,为了屏幕尺寸的最大化,窄边框的显示面板广泛地应用于各种装置上。目前已发展出栅极驱动电路技术(gate driver on array,goa),此技术是将显示面板的栅极驱动电路制作于显示面板的周边区,以代替外接的驱动芯片的技术。然而,当大尺寸的显示面板操作于高电压及高电流的状况下,栅极驱动电路的元件容易发生自热效应(self-heating effect),导致此元件发生劣化。因此,目前亟需一种能解决前述问题的方法。

技术实现要素:

3.本发明提供一种栅极驱动装置,具有提升的可靠度。

4.本发明的一种栅极驱动装置包括玻璃基板及多个移位暂存器。移位暂存器形成于玻璃基板上且每级相互串联耦接,并分别产生多个栅极驱动信号,第n级的移位暂存器包括上拉单元。上拉单元具有控制端以接收控制信号,依据控制信号以提供时钟信号至输出端以产生第n级栅极驱动信号,上拉单元包括多个第一晶体管及多个第二晶体管。第一晶体管位于上拉单元的最外侧,各第一晶体管沿着列方向具有长度l1。第二晶体管被第一晶体管环绕,其中各第二晶体管沿着列方向具有长度l2,且满足n*l1+(n-1)*(x2-x1)=m*l2+(m-1)*x2,各第一晶体管与其相邻的第二晶体管其中之一沿着列方向具有间距x1,各第二晶体管之间沿着列方向具有间距x2,且满足x2》(x1-x2)*1.3。

5.本发明的一种栅极驱动装置包括基板及多个移位暂存器。移位暂存器形成于玻璃基板上且每级相互串联耦接,并分别产生多个栅极驱动信号,第n级的移位暂存器包括上拉单元。上拉单元具有控制端以接收控制信号,依据控制信号以提供时钟信号至输出端以产生第n级栅极驱动信号,上拉单元包括多个第一晶体管及多个第二晶体管。第一晶体管位于上拉单元的最外侧。第二晶体管被第一晶体管环绕,各第一晶体管和与其相邻的第二晶体管其中之一沿着行方向错位。

6.本发明提供一种显示面板具有显示区及周边区,周边区位于显示区的至少一侧且包括如前述的栅极驱动装置及像素阵列。前述的栅极驱动装置位于周边区。像素阵列位于显示区。

7.基于上述,在本发明一实施例的栅极驱动装置中,第二晶体管被第一晶体管环绕,其中各第二晶体管沿着列方向具有长度l2,且满足n*l1+(n-1)*(x2-x1)=m*l2+(m-1)*x2,各第一晶体管与其相邻的第二晶体管其中之一沿着列方向具有间距x1,各第二晶体管之间沿着列方向具有间距x2,且满足x2》(x1-x2)*1.3,因此可以增加上拉单元中央的散热面积,避免上拉单元中央因为自热效应对其电性造成负面影响。因此,本发明的栅极驱动装置具有提升的可靠度。基于类似的理由,本发明的显示面板具有提升的可靠度。

附图说明

8.阅读以下详细叙述并搭配对应的附图,可了解本公开的多个样态。需留意的是,附图中的多个特征并未依照该业界领域的标准作法绘制实际比例。事实上,所述的特征的尺寸可以任意的增加或减少以利于讨论的清晰性。

9.图1是依照本发明一实施例的栅极驱动装置的俯视示意图。

10.图2为依照本发明一实施例的栅极驱动装置的电路方框示意图。

11.图3是第n级的移位暂存器的等效电路示意图。

12.图4是图3的第n级的移位暂存器的时序图。

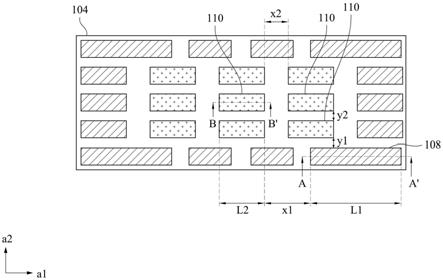

13.图5是上拉单元的电路布局俯视示意图。

14.图6是图5沿着剖线a-a’的剖面示意图。

15.图7是图5沿着剖线b-b’的剖面示意图。

16.图8是依照本发明另一实施例的第一晶体管的俯视示意图。

17.图9是图8的剖线c-c’的剖面示意图。

18.图10是依照本发明另一实施例的第二晶体管的俯视示意图。

19.图11是图10的剖线d-d’的剖面示意图。

20.图12是依照本发明另一实施例的栅极驱动装置的上拉单元的俯视示意图。

21.图13是对比例的上拉单元的俯视示意图。

22.图14是依照本发明另一实施例的栅极驱动装置的上拉单元的俯视示意图。

23.图15是图12沿剖线e-e’的剖面示意图。

24.图16是图12沿剖线f-f’的剖面示意图。

25.图17是依照本发明一实施例的显示面板的俯视示意图。

26.图18示出图17的像素阵列的部分剖面图及栅极驱动装置的部分剖面图。

27.附图标记说明:

28.10,20,42

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

:

ꢀꢀꢀꢀ

栅极驱动装置

29.40

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

:

ꢀꢀꢀꢀ

显示面板

30.100

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

:

ꢀꢀꢀꢀ

基板

31.102

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

:

ꢀꢀꢀꢀ

上拉控制单元

32.104,204,204a,304

ꢀꢀꢀꢀꢀ

:

ꢀꢀꢀꢀ

上拉单元

33.106

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

:

ꢀꢀꢀꢀ

下拉单元

34.108,108a,208,208a

ꢀꢀꢀꢀ

:

ꢀꢀꢀꢀ

第一晶体管

35.110,110a,210,210a

ꢀꢀꢀꢀ

:

ꢀꢀꢀꢀ

第二晶体管

36.308,408

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

:

ꢀꢀꢀꢀ

第一晶体管

37.310,410

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

:

ꢀꢀꢀꢀ

第二晶体管

38.112

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

:

ꢀꢀꢀꢀ

闸绝缘层

39.114

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

:

ꢀꢀꢀꢀ

层间介电层

40.116

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

:

ꢀꢀꢀꢀ

绝缘层

41.a1

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

:

ꢀꢀꢀꢀ

第一方向

42.a2

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

:

ꢀꢀꢀꢀ

第二方向

43.a3

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

:

ꢀꢀꢀꢀ

第三方向

44.a4

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

:

ꢀꢀꢀꢀ

第四方向

45.aa

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

:

ꢀꢀꢀꢀ

显示区

46.ar

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

:

ꢀꢀꢀꢀ

像素阵列

47.a-a’,b-b

’ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

:

ꢀꢀꢀꢀ

剖线

48.ch1,ch2,ch5

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

:

ꢀꢀꢀꢀ

通道层

49.ck

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

:

ꢀꢀꢀꢀ

时钟信号

50.c-c’,d-d’,e-e’,f-f

’ꢀꢀꢀꢀ

:

ꢀꢀꢀꢀ

剖线

51.d1,d1a,d1b,d1c

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

:

ꢀꢀꢀꢀ

漏极

52.d2,d2a,d2b,d2c,d5

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

:

ꢀꢀꢀꢀ

漏极

53.d1,d2,d3,d4,d5,d6,d7

ꢀꢀꢀꢀꢀꢀꢀ

:

ꢀꢀꢀꢀ

距离

54.d8,d9,d10,d11,d12

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

:

ꢀꢀꢀꢀ

距离

55.g1,g1a,g1b,g1c

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

:

ꢀꢀꢀꢀ

栅极

56.g2,g2a,g2c,g5

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

:

ꢀꢀꢀꢀ

栅极

57.g[n]

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

:

ꢀꢀꢀꢀ

第n级栅极驱动信号

[0058]

g[n-1],g[n+1]

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

:

ꢀꢀꢀꢀ

输入信号

[0059]

gout[n]

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

:

ꢀꢀꢀꢀ

输出端

[0060]

l1,l2

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

:

ꢀꢀꢀꢀ

长度

[0061]

pa

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

:

ꢀꢀꢀꢀ

周边区

[0062]

pe

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

:

ꢀꢀꢀꢀ

像素电极

[0063]

px

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

:

ꢀꢀꢀꢀ

像素

[0064]

qn

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

:

ꢀꢀꢀꢀ

节点

[0065]

r1

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

:

ꢀꢀꢀꢀ

区域

[0066]

s1,s1a,s1b,s1c

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

:

ꢀꢀꢀꢀ

源极

[0067]

s2,s2a,s2c,s5

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

:

ꢀꢀꢀꢀ

源极

[0068]

sr

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

:

ꢀꢀꢀꢀ

移位暂存器

[0069]

stv

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

:

ꢀꢀꢀꢀ

起动脉冲

[0070]

t1

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

:

ꢀꢀꢀꢀ

第一开关

[0071]

t2

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

:

ꢀꢀꢀꢀ

第二开关

[0072]

t3

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

:

ꢀꢀꢀꢀ

第三开关

[0073]

t4

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

:

ꢀꢀꢀꢀ

第四开关

[0074]

t5

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

:

ꢀꢀꢀꢀ

主动元件

[0075]

x1,x2,x3,y1,y2

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

:

ꢀꢀꢀꢀ

间距

具体实施方式

[0076]

以下将参照本实施例的附图以更全面地阐述本发明。然而,本发明亦可以各种不同的形式体现,而不应限于本文中所述的实施例。附图中的各构件的尺寸和厚度会为了清楚起见而进行适当的调整,本发明不以此为限。相同或相似的参考号码表示相同或相似的元件,以下段落将不再一一赘述。另外,实施例中所提到的方向用语,例如:上、下、左、右、前或后等,仅是参考附加附图的方向。因此,使用的方向用语是用来说明并非用来限制本发

明。

[0077]

图1是依照本发明一实施例的栅极驱动装置10的俯视示意图。栅极驱动装置10包括玻璃基板100及多个移位暂存器sr,移位暂存器sr形成于玻璃基板100上且每级相互串联耦接,并分别产生多个栅极驱动信号。

[0078]

图2为依照本发明一实施例的栅极驱动装置10的电路方框示意图,请一并参照图1及图2,在本实施例中,栅极驱动装置10的各移位暂存器sr分别有一个起动脉冲,表示为stv。在本实施例中,当开始进行一个图框的驱动时,启动脉冲stv会被致能。栅极驱动装置10具有至少一汇流线(bus line;未示)。汇流线(未示)用以接收时钟信号ck。移位暂存器sr接收来自汇流线(未示)的时钟信号ck后,将时钟信号ck转换为对应扫描线(未示)的栅极驱动信号g1-gn,并产生用以传递至下一级的移位暂存器sr的推动信号,进而周而复始地驱动所有扫描线(未示)。直到最后一个移位暂存器sr输出栅极驱动信号gn后,时钟信号ck被禁能。但本发明不以此为限,移位暂存器sr还可具有其他电极结构或元件。

[0079]

图3是第n级的移位暂存器sr的等效电路示意图,图4是图3的第n级的移位暂存器sr的时序图,请参照图3及图4,第n级的移位暂存器sr包括上拉控制单元102、上拉单元104及下拉单元106。上拉控制单元102包括第一开关t1,上拉单元104包括第二开关t2,下拉单元106包括第三开关t3及第四开关t4。

[0080]

上拉单元104具有控制端以接收控制信号,依据控制信号以提供时钟信号至输出端以产生一第n级栅极驱动信号g[n]。举例而言,第一开关t1接收输入信号g[n-1],第二开关t2接收输入信号g[n+1]。输入信号g[n-1]及输入信号g[n+1]来自于前一级和后一级的移位暂存器sr的输入端。第二开关t2的第一端(可以是源/漏极端其中之一)接收时钟信号ck,第二开关t2的控制端耦接于节点qn,而第二开关t2的第二端(可以是源/漏极端其中另一)耦接于第n级移位暂存器sr的输出端gout[n],以输出第n级栅极驱动信号g[n]。

[0081]

第四开关t4的第一端耦接于节点qn,第三开关t3的第一端耦接于移位暂存器sr的输出端gout[n],第四开关t4的第二端及第三开关t3的第二端皆耦接于系统电压端vss。系统电压端vss的电位可与栅极低电压vgl相同。输入信号g[n+1]被传送到第四开关t4的控制端及第三开关t3的控制端,以控制第四开关t4及第三开关t3的开启和关闭。时钟信号ck会在栅极高电压vgh及栅极低电压vgl之间切换。

[0082]

图5是上拉单元104的电路布局俯视示意图。图6是图5沿着剖线a-a’的剖面示意图。图7是图5沿着剖线b-b’的剖面示意图。请一并参照图5至图7,上拉单元104包括多个第一晶体管108及多个第二晶体管110。换言之,由多个第一晶体管108及多个第二晶体管110构成第二开关t2(见图3)。第一晶体管108位于上拉单元104的最外侧。举例而言,第一晶体管108的至少一侧无配置第一晶体管108且无配置第二晶体管110。各第一晶体管108沿着列方向具有长度l1。为了方便说明,图5中示出了第一方向a1及第二方向a2,第一方向a1和第二方向a2相交。举例而言,第一方向a1和第二方向a2可实质上互相垂直。于本实施例中,列方向例如是图5中的第一方向a1。第二晶体管110被第一晶体管108环绕。举例而言,第二晶体管110的四侧皆配置第二晶体管110或第一晶体管108。其中每一第二晶体管110沿着列方向具有长度l2,且满足n*l1+(n-1)*(x2-x1)=m*l2+(m-1)*x2,各第一晶体管108与其相邻的第二晶体管110其中之一沿着列方向具有间距x1。每一第二晶体管110之间沿着列方向具有间距x2,且满足x2》(x1-x2)*1.3。因此,在几乎不影响上拉单元104在移位暂存器sr(见图

1)的占地面积的状况下,可以增加上拉单元104中央的散热面积,避免上拉单元104中央因为自热效应(self-heating effect)对其电性造成负面影响,使栅极驱动装置10(见图1)提升其可靠度。举例而言,可避免自热效应所造成的第二晶体管110的阈值电压(threshold voltage;vth)的改变,且可降低自热效应所造成的第二晶体管110的启动电流(ion)的劣化程度。当栅极驱动装置10(见图1)应用于需要高电压及高电流来操作的大尺寸的显示面板时,可有效降低上述的自热效应所造成的负面影响。

[0083]

第一晶体管108可包括源极s1、漏极d1、栅极g1与通道层ch1。各第一晶体管108沿着列方向的长度l1等同于其通道层ch1沿着列方向的长度。第二晶体管110可包括源极s2、漏极d2、栅极g2与通道层ch2。各第二晶体管110沿着列方向的长度l2等同于其通道层ch2沿着列方向的长度。基于电子迁移率的考量,通道层ch1及通道层ch2的材料包括低温多晶硅(low temperature crystalline silicon,ltps)、氧化物半导体(例如是铟镓锌氧化物(indium gallium zinc oxide,igzo)等)或其类似者。通道层ch1及通道层ch2配置于玻璃基板100上。

[0084]

上拉单元104还包括闸绝缘层112、层间介电层114及绝缘层116。闸绝缘层112配置于通道层ch1及栅极g1之间以及通道层ch2及栅极g2之间。举例而言,在本实施例中,第一晶体管108的栅极g1配置于通道层ch1的上方,第二晶体管110的栅极g2配置于通道层ch2的上方,以形成顶部栅极型薄膜晶体管(top-gate tft),但本发明不以此为限。根据其他的实施例,第一晶体管108的栅极g1亦可配置在通道层ch1的下方,第二晶体管110的栅极g2亦可配置在通道层ch2的下方,即栅极g1、栅极g2位于通道层ch1、通道层ch2与玻璃基板100之间,以形成底部栅极型薄膜晶体管(bottom-gate tft)。

[0085]

层间介电层114覆盖栅极g1、g2,源极s1、s2与漏极d1、d2贯穿层间介电层114及闸绝缘层112以分别与通道层ch1、ch2电性连接。绝缘层116配置于层间介电层114上,以覆盖源极s1、s2与漏极d1、d2。在本实施例中,闸绝缘层112、层间介电层114以及绝缘层116的材料可为无机材料或有机材料或上述组合。无机材料例如是氧化硅、氮化硅、氮氧化硅或上述至少二种材料的堆叠层,但本发明不以此为限。

[0086]

于本实施例中,各第一晶体管108和与其相邻的第二晶体管110其中之一沿着行方向具有间距y1,且满足x2》y1。于本实施例中,行方向例如是图5中的第二方向a2。因此,可以增加上拉单元104中央的散热面积。

[0087]

于本实施例中,各第二晶体管110沿着行方向具有间距y2,且满足y2》y1。举例而言,满足y2》1.3*y1。因此,可以增加上拉单元104中央的散热面积。

[0088]

图8是依照本发明另一实施例的第一晶体管108a的俯视示意图,图9是图8的剖线c-c’的剖面示意图,本实施例的第一晶体管108a与图6的第一晶体管108的差异在于本实施例的第一晶体管108a具有第一栅极g1a、第一源极s1a与第一漏极d1a,第一漏极d1a与第一栅极g1a之间的距离d1大于第一源极s1a与第一栅极g1a之间的距离d2。因此,可使第一漏极d1a有效散热。当栅极驱动装置10应用于需要高电压及高电流来操作的大尺寸的显示面板时,可有效降低第一晶体管108a的第一漏极d1a因上述的自热效应所造成的负面影响,且采用本实施例的第一晶体管108a的上拉单元适用于单向操作。

[0089]

图10是依照本发明另一实施例的第二晶体管110a的俯视示意图,图11是图10的剖线d-d’的剖面示意图,本实施例的第二晶体管110a与图7的第二晶体管110的差异在于本实

施例的第二晶体管110a具有第二栅极g2a、第二源极s2a与第二漏极d2a,第二漏极d2a与第二栅极g2a之间的距离d3大于第二源极s2a与第二栅极g2a之间的距离d4。因此,可使第二漏极d2a有效散热。当栅极驱动装置10应用于需要高电压及高电流来操作的大尺寸的显示面板时,可有效降低第二晶体管110a的第二漏极d2a因上述的自热效应所造成的负面影响,且采用本实施例的第二晶体管110a的上拉单元适用于单向操作。

[0090]

图12是依照本发明另一实施例的栅极驱动装置20的上拉单元204的俯视示意图,图13是对比例的上拉单元304的俯视示意图。请先参照图12,本实施例的上拉单元204包括多个第一晶体管208及多个第二晶体管210。第一晶体管208位于上拉单元204的最外侧。第二晶体管210被第一晶体管208环绕,其中各第一晶体管208和与其相邻的第二晶体管210其中之一沿着行方向错位。接着,请参照图13,对比例的第一晶体管308和与其相邻的第二晶体管310其中之一没有沿着行方向错位。如图12及图13所示,将上拉单元204及上拉单元304沿着列方向划分为多个具有长方形形状的区域r1时,图12的第一晶体管208及第二晶体管210在各个区域r1的覆盖面积小于图13的第一晶体管308及第二晶体管310在各个区域r1的覆盖面积。换言之,本实施例的上拉单元204的第一晶体管208及第二晶体管210的占用面积相较于对比例的上拉单元304的第一晶体管308及第二晶体管310的占用面积小,因此,本实施例的上拉单元204散热面积增加,且第一晶体管208及与其相邻的第二晶体管210其中之一的间距x3增加,因此可避免上拉单元204中央因为自热效应对其电性造成负面影响,使栅极驱动装置提升其可靠度。此处的间距x3指的是,在俯视图中,第一晶体管208的顶侧及与其相邻的第二晶体管210的顶侧的连线距离或是第一晶体管208的底侧及与其相邻的第二晶体管210的底侧的连线距离。本实施例的栅极驱动装置的其他构件类似于图1的栅极驱动装置,于此不再赘述。

[0091]

图14是依照本发明另一实施例的栅极驱动装置的上拉单元204a的俯视示意图。本实施例的上拉单元204a与图12的上拉单元204的差异在于各第二晶体管210a排列成第1~n行,n为大于或等于2的正整数,相邻的两行所具有的第二晶体管210a沿着行方向错位。如前所述,可避免上拉单元204a中央因为自热效应对其电性造成负面影响,使栅极驱动装置提升其可靠度。

[0092]

请回到图12,图12的第一晶体管208的结构可类似于图6的第一晶体管108或图9的第一晶体管108a的结构,图12的第二晶体管210的结构可类似于图7的第二晶体管110或图11的第二晶体管110a的结构。举例而言,图15是图12沿剖线e-e’的剖面示意图,图16是图12沿剖线f-f’的剖面示意图,且图15及图16示出了图12的第一晶体管208的结构及第二晶体管210的结构分别类似于图9及图11的第一晶体管108a的结构及第二晶体管110a的结构的例子,请参照图15及图16,各第一晶体管208具有第一栅极g1b、第一源极s1b与第一漏极d1b,第一漏极d1b与第一栅极g1b之间的距离d5大于第一源极s1b与第一栅极g1b之间的距离d6。各第二晶体管210具有第二栅极g2b、第二源极s2b与第二漏极d2b,第二漏极d2b与第二栅极g2b之间的距离d7大于第二源极s2b与第二栅极g2b之间的距离d8。如此一来,因此,可使第一漏极d1b及第二漏极d2b有效散热。当栅极驱动装置应用于需要高电压及高电流来操作的大尺寸的显示面板时,可有效降低第一晶体管208的第一漏极d1b及第二晶体管210的第二漏极d2b因上述的自热效应所造成的负面影响,且采用本实施例的第一晶体管208及第二晶体管210的上拉单元204适用于单向操作。

[0093]

图17是依照本发明一实施例的显示面板40的俯视示意图。显示面板40具有显示区aa及周边区pa,周边区pa位于显示区aa的至少一侧。显示面板40包括至少一个栅极驱动装置42,栅极驱动装置10位于周边区pa。像素阵列ar位于显示区aa。栅极驱动装置42的配置类似于先前实施例的栅极驱动装置10,因此基于类似的理由,本发明的显示面板40具有提升的可靠度。

[0094]

图18示出图17的像素阵列ar的部分剖面图及栅极驱动装置42的部分剖面图。请一并参考图17及图18,如同之前所述,栅极驱动装置42包括多个第一晶体管408及多个第二晶体管410。于一实施例中,第一晶体管408具有第一栅极g1c、第一源极s1c与第一漏极d1c,第一漏极d1c与第一栅极g1c之间的距离d9大于第一源极s1c与第一栅极g1c之间的距离d10。因此,可使第一漏极d1c有效散热。当栅极驱动装置42应用于需要高电压及高电流来操作的大尺寸的显示面板时,可有效降低第一晶体管408的第一漏极d1c因上述的自热效应所造成的负面影响,且本实施例的栅极驱动装置42适用于单向操作。第二晶体管410具有第二栅极g2c、第二源极s2c与第二漏极d2c,第二漏极d2c与第二栅极g2c之间的距离d11大于第二源极s2c与第二栅极g2c之间的距离d12。因此,可使第二漏极d2c有效散热。当栅极驱动装置42应用于需要高电压及高电流来操作的大尺寸的显示面板时,可有效降低第二晶体管410的第二漏极d2c因上述的自热效应所造成的负面影响,且本实施例的栅极驱动装置42适用于单向操作。

[0095]

像素阵列ar包括多个像素px。为了方便说明,图17中示出了第三方向a3与第四方向a4,且第三方向a3与第四方向a4相异,例如第三方向a3与第四方向a4分别为图17的横向方向与纵向方向,且其彼此呈正交关系。各像素px沿着第三方向a3及第四方向a4排列。

[0096]

各像素px可包括主动元件t5及电性连接至主动元件t5的像素电极pe。主动元件t5配置于玻璃基板100上,且具有栅极g5、源极s5、漏极d5以及通道层ch5。闸绝缘层112配置于通道层ch5及栅极g5之间。举例而言,主动元件t5的栅极g5可选择性地配置于通道层ch5的上方,以形成顶部栅极型薄膜晶体管(top gate tft),但本发明不以此为限。根据其他的实施例,主动元件t5的栅极g5也可配置在通道层ch5的下方,即栅极g5位于通道层ch5与玻璃基板100之间,以形成底部栅极型薄膜晶体管(bottom gate tft)。

[0097]

基于电子迁移率的考量,主动元件t5的通道层ch5的材料包括低温多晶硅(low temperature crystalline silicon,ltps)、氧化物半导体(例如是铟镓锌氧化物(indium gallium zinc oxide,igzo)等)或其类似者。通道层ch5配置于玻璃基板100上。于本实施例中,第一晶体管108的通道层ch1及主动元件t5的通道层ch5其中一者为低温多晶硅(low temperature crystalline silicon,ltps),其中另一者为氧化物半导体(例如是铟镓锌氧化物(indium gallium zinc oxide,igzo)等),也就是说,显示面板40为低温多晶氧化物(low temperature polycrystalline oxide,ltpo)显示面板。

[0098]

层间介电层114覆盖主动元件t5的栅极g5。主动元件t5的源极s5与漏极d5配置于层间介电层114上。举例而言,主动元件t5的源极s5与漏极d5都贯穿层间介电层114以及闸绝缘层112,以电性连接通道层ch5。

[0099]

综上所述,在本发明一实施例的栅极驱动装置中,第二晶体管被第一晶体管环绕,其中各第二晶体管沿着列方向具有长度l2,且满足n*l1+(n-1)*(x2-x1)=m*l2+(m-1)*x2,各第一晶体管与其相邻的第二晶体管其中之一沿着列方向具有间距x1,各第二晶体管之间

沿着列方向具有间距x2,且满足x2》(x1-x2)*1.3,因此可以增加上拉单元中央的散热面积,避免上拉单元中央因为自热效应对其电性造成负面影响。因此,本发明的栅极驱动装置具有提升的可靠度。基于类似的理由,本发明的显示面板具有提升的可靠度。