像素电路和使用其的显示装置

1.相关申请的交叉引用

2.本技术要求2020年8月20日提交的韩国专利申请第10-2020-0104740号的优先权和权益,其全部内容通过引用合并于此。

技术领域

3.本公开内容涉及其中像素驱动电压被提供至所有像素的像素电路的显示装置。

背景技术:

4.根据发光层的材料,电致发光显示装置大致分为无机发光显示装置和有机发光显示装置。有源矩阵形式的有机发光显示装置包括有机发光二极管(以下称为oled),其被配置成自发光并且具有诸如高响应速度、高发光效率、高亮度和宽视角的优点。在有机发光显示装置中,oled形成在像素中的每个像素中。有机发光显示装置不仅可以具有高响应速度、高发光效率、高亮度和宽视角,而且可以在全黑中表现出黑色渐变,因此可以具有高的对比率和色彩再现率。

5.有机发光显示装置不需要背光单元,并且可以在由柔性材料制成的塑料基板、薄玻璃基板或金属基板上实现。因此,可以使用有机发光显示装置来实现柔性显示器。

6.在柔性显示器中,屏幕的尺寸和形状以使显示面板卷曲、折叠或弯曲的方式可变。柔性显示器可以被实现为可卷曲显示器、可弯曲显示器、可折叠显示器、可滑动显示器等。这样的柔性显示器不仅可以应用于诸如智能电话和平板个人计算机(pc)的移动设备,而且可以应用于电视(tv)、车辆显示器和可穿戴设备,并且其应用领域正在扩大。

7.有机发光显示装置的像素均包括:oled;驱动元件,其通过根据栅极-源极电压(vgs)控制在oled中流动的电流来驱动oled;以及存储电容器,其保持该驱动元件的栅极电压。

8.驱动元件可以被实现为晶体管。为了使有机发光显示装置的整个屏幕的图像质量均匀,所有像素的驱动元件应具有均匀的电特性。然而,由于在显示面板的制造过程中引起的工艺偏差和元件特性偏差,像素的驱动元件可能在电特性方面具有差异,并且随着像素的驱动时间的流逝,差异可能会增加。为了补偿像素的驱动元件之间的电特性偏差,可以将内部补偿技术或外部补偿技术应用于有机发光显示装置。

9.在内部补偿技术中,使用内置在像素中的每个像素中的内部补偿电路对于每个子像素采样驱动元件的阈值电压,从而对驱动元件的栅极-源极电压(vgs)补偿阈值电压这么多。在外部补偿技术中,使用外部补偿电路实时感测根据驱动元件的电特性而变化的驱动元件的电流或电压。在外部补偿技术中,对输入图像的像素数据(数字数据)进行调制达对于每个像素被感测的驱动元件的电特性偏差(或变化)之多,从而在像素中的每个像素中实时补偿驱动元件的电特性偏差(或变化)。

技术实现要素:

10.由于有机发光二极管(oled)的效率的提高,在低灰度下流向oled的电流可能减少。这是因为oled的寄生电容充电的时间由于低电流而延迟。因此,在具有高效率的oled中,低灰度表现特性可能劣化,并且在低速驱动模式下可以看到亮度时段性波动的闪烁。

11.本公开内容的目的是解决上述需求和/或问题。

12.本公开内容旨在提供一种像素电路以及使用该像素电路的显示装置,该像素电路在低速驱动模式下具有改善的低灰度表现特性以及减少的闪烁。

13.应当注意,本公开内容的目的不限于上述目的,并且根据以下描述,本公开内容的其他目的对于本领域技术人员将是明显的。

14.根据本公开内容的一方面,提供了一种像素电路,该像素电路包括:发光元件,其包括阳极与阴极;驱动元件,其包括连接至第一节点的栅电极;连接至第二节点的第一电极;以及第二电极,其连接至第三节点并向发光元件提供电流;第一开关元件,其被配置成在采样步骤中将第一节点连接至第三节点;第二开关元件,其被配置成在采样步骤中向第二节点提供数据电压;第三开关元件,其被配置成在采样步骤之后的发光步骤中向第二节点提供像素驱动电压;第四开关元件,其被配置成在发光步骤中将第三节点连接至发光元件的阳极;第一电容器,其连接至第一节点;第二电容器,其连接在第三节点与发光元件的阳极之间;以及第三电容器,其连接在发光元件的阳极与阴极之间。

15.根据本公开内容的一方面,提供了一种包括上述像素电路的显示装置。

16.根据本公开内容的一方面,提供了一种显示装置,包括:数据驱动器,其被配置成将数据电压提供至数据线;栅极驱动器,其被配置成在初始化步骤中将生成为栅极导通电压的脉冲的第n-1扫描信号提供至第一栅极线,在所述初始化步骤之后的采样步骤中将生成为所述栅极导通电压的所述脉冲的第n扫描信号提供至第二栅极线,以及在所述采样步骤之后的发光步骤中将生成为所述栅极导通电压的发光信号提供至第三栅极线,其中,n是大于或等于1的正整数;电源,其被配置成输出像素驱动电压以及低于所述像素驱动电压的低电位电力电压和初始化电压;以及包括连接至所述数据线和所述第一栅极线至所述第三栅极线的像素电路的红色子像素、绿色子像素和蓝色子像素,其中,所述像素电路包括:发光元件,其包括阳极与阴极;驱动元件,其包括连接至第一节点的栅电极、连接至第二节点的第一电极、以及连接至第三节点并将电流提供至所述发光元件的第二电极;第一开关元件,其被配置成在所述采样步骤中将所述第一节点连接至所述第三节点;第二开关元件,其被配置成在所述采样步骤中将所述数据电压提供至所述第二节点;第三开关元件,其被配置成在所述采样步骤之后的发光步骤中将所述像素驱动电压提供至所述第二节点;第四开关元件,其被配置成在所述发光步骤中将所述第三节点连接至所述发光元件的所述阳极;第一电容器,其连接至所述第一节点;第二电容器,其连接在所述第三节点与所述发光元件的所述阳极之间;以及第三电容器,其连接在所述发光元件的所述阳极与所述阴极之间。

附图说明

17.图1是示出根据本公开内容的实施方式的显示装置的框图。

18.图2是示出像素阵列的一些像素和线的示意图。

19.图3是示出本公开内容的像素电路的示意图。

20.图4是示出具有串联结构的发光元件的示例的截面图。

21.图5是示出在效率提高的发光元件中降低低灰度下的亮度的示例的曲线图。

22.图6图示了示出根据本公开内容的第一实施方式的像素电路的电路图。

23.图7图示了示出图6所示的像素电路的驱动方法的电路图。

24.图8是示出根据本公开内容的第二实施方式的像素电路的电路图。

25.图9a至图11b是顺序示出图8所示的像素电路的操作的图。

26.图12是示出根据本公开内容的第三实施方式的像素电路的电路图。

27.图13是示出图12所示的像素电路的驱动方法的波形图。

具体实施方式

28.从下面参考附图描述的实施方式中,将更加清楚地理解本公开内容的优点和特征以及用于实现本公开内容的方法。然而,本公开内容不限于以下实施方式,而是可以以各种不同的形式来实现。相反,本实施方式将使本公开内容的公开完整,并使本领域技术人员能够完全理解本公开内容的范围。本公开内容仅在所附权利要求的范围内定义。

29.在附图中示出的用于描述本公开内容的实施方式的形状、尺寸、比率、角度、数量等仅是示例,并且本公开内容不限于此。在整个本说明书中,相同的附图标记通常表示相同的元件。此外,在描述本公开内容时,可以省略已知相关技术的详细描述,以避免不必要地使本公开内容的主题不清楚。

30.本文使用的诸如“包括”、“包含”、“具有”和“由...组成”之类的术语通常旨在允许添加其他部件,除非该术语与术语“仅”一起使用。除非另有明确说明,否则对单数的任何提及均可以包括复数。

31.即使没有明确说明,部件也会被解释为包括普通的误差范围。

32.当使用诸如“在...上”、“在...上方”、“在...下面”和“旁边”之类的术语描述两个部件之间的位置关系时,一个或更多个部件可以位于这两个部件之间,除非这些术语与术语“紧接”或“直接”一起使用。

33.术语“第一”、“第二”等可以用于将部件彼此区分开,但是部件的功能或结构不受部件前面的序号或部件名称的限制。

34.以下实施方式可以部分或全部彼此结合或组合,并且可以技术上以各种方式联系和操作。实施方式可以彼此独立地或彼此关联地执行。

35.在本公开内容的显示装置中,像素电路可以包括n沟道晶体管和p沟道晶体管中的至少一个。晶体管可以被实现为包括氧化物半导体的氧化物薄膜晶体管(氧化物tft)、包括低温多晶硅的低温多晶硅(ltps)tft等。此外,晶体管中的每个晶体管可以被实现为p沟道tft或n沟道tft。在实施方式中,将基于其中像素电路的晶体管被实现为p沟道tft的示例给出描述,但是本公开内容不限于此。

36.晶体管是包括栅极、源极和漏极的三电极元件。源极是向晶体管提供载流子的电极。在晶体管中,载流子从源极开始流动。漏极是载流子通过其从晶体管离开的电极。在晶体管中,载流子从源极流到漏极。在n沟道晶体管的情况下,由于载流子是电子,源极电压是低于漏极电压的电压,使得电子可以从源极流到漏极。n沟道晶体管具有从漏极流向源极的电流方向。在p沟道晶体管(p沟道金属氧化物半导体(pmos))的情况下,由于载流子是空穴,

源极电压高于漏极电压,使得空穴可以从源极流到漏极。在p沟道晶体管中,由于空穴从源极流到漏极,电流从源极流到漏极。应当注意,晶体管的源极和漏极不是固定的。例如,可以根据施加的电压来改变源极和漏极。因此,本公开内容不受晶体管的源极和漏极的限制。在下面的描述中,将晶体管的源极和漏极称为第一电极和第二电极。

37.栅极信号在栅极导通电压与栅极截止电压之间摆动。栅极导通电压被设置为高于晶体管的阈值电压的电压,并且栅极截止电压被设置为低于晶体管的阈值电压的电压。响应于栅极导通电压而使晶体管导通,以及响应于栅极截止电压而使晶体管截止。在n沟道晶体管的情况下,栅极导通电压可以是栅极高电压vgh,而栅极截止电压可以是栅极低电压vgl。在p沟道晶体管的情况下,栅极导通电压可以是栅极低电压vgl,而栅极截止电压可以是栅极高电压vgh。

38.在下文中,将参考附图详细描述本公开内容的各种实施方式。

39.图1是示出根据本公开内容的实施方式的显示装置的框图。图2是示出像素阵列的一些像素和线的示意图。在图2中,省略了电力线。

40.参照图1和图2,根据本公开内容实施方式的显示装置包括显示面板100和用于将输入图像的像素数据写入显示面板100的像素的显示面板驱动器。

41.显示面板100包括在屏幕上显示输入图像的像素阵列。像素阵列包括多条数据线dl、与数据线dl相交的多条栅极线gl、以及设置成由数据线dl和栅极线gl限定的矩阵形式的像素。

42.像素中的每个像素可以被划分为红色、绿色和蓝色子像素101,以表示颜色。像素中的每个像素还可以包括白色子像素。子像素101中的每个子像素包括驱动发光元件oled的像素电路。另外,子像素101可以包括滤色器,但是在移动设备的情况下,可以省略滤色器。在下文中,像素可以被解释为具有与子像素相同的含义。

43.像素阵列包括多条像素线l1至ln。像素线包括设置在沿行线方向(x轴方向)设置的一条线上的像素。当像素阵列具有m

×

n的分辨率时,像素阵列包括n条像素线l1至ln。设置在一条像素线上的像素共享栅极线并且连接至不同的数据线dl。在列方向(y轴方向)上垂直设置的子像素101共享相同的数据线。

44.触摸传感器可以被设置在显示面板100的屏幕上。触摸传感器可以被设置为显示面板100的屏幕上的单元上(on-cell)类型或附加(add-on)类型,或者可以被实现为内置在像素阵列中的单元内(in-cell)类型的触摸传感器。

45.显示面板驱动器将输入图像的像素数据写入子像素101以在显示面板100的屏幕上再现输入图像。显示面板驱动器包括数据驱动器110、栅极驱动器120和定时控制器130。显示面板驱动器还可以包括设置在数据驱动器110与数据线dl之间的解复用器112。

46.显示面板驱动器可以在低速驱动模式下操作。在低速驱动模式下,当输入图像被分析并且因此在预设时间内没有改变时,可以减少显示装置的功耗。在低速驱动模式下,当在预定时间或更长时间内输入静止图像时,像素的刷新率降低以将像素的数据写入时段控制成更长,从而降低功耗。低速驱动模式不限于输入静止图像的情况。例如,当显示装置在待机模式下操作时或者当用户命令或输入图像在预定时间或更长时间内没有被输入至显示面板驱动器时,显示面板驱动器可以在低速驱动模式下操作。

47.数据驱动器110通过使用数模转换器(以下称为“dac”)将作为数字数据的输入图

像的像素数据转换成伽马补偿电压来生成数据电压vdata。伽马补偿电压通过从分压器电路输出而被输入至dac,该分压器电路对伽马参考电压gma进行分压,以生成每个灰度的电压。数据电压vdata可以通过解复用器112被提供至显示面板100的数据线dl。

48.当像素电路的驱动元件被实现为p沟道晶体管时,白色灰度电压是在从数据驱动器110输出的像素数据的电压范围内的最小电压。例如,可以将像素数据的白色灰度电压设置为0v,并且可以将其黑色灰度电压设置为5v,但是本公开内容不限于此。

49.解复用器112对通过数据驱动器110的一个通道输出的数据电压vdata进行时分,以将时分的数据电压vdata分配至多条数据线dl。由于解复用器112,可以减少数据驱动器110的通道的数量。

50.栅极驱动器120可以被实现为与像素阵列的tft阵列一起直接形成在显示面板100的边框区域bz上的板内栅极(gate-in panel,gip)电路。栅极驱动器120在定时控制器130的控制下将栅极信号输出至栅极线gl。栅极驱动器120可以使用移位寄存器将栅极信号g1至g(n)移位以顺序地将信号提供至栅极线gl。栅极信号g1包括扫描信号scan0和scan1以及em信号(发光信号)em1,栅极信号g2包括扫描信号scan1和scan2以及em信号em2,

…

,栅极信号g(n)包括扫描信号scan(n-1)和scan(n)以及em信号em(n)。n是大于或等于1的正整数。栅极信号g1至g(n)的电压在栅极截止电压vgh与栅极导通电压vgl之间摆动。

51.栅极驱动器120可以包括第一栅极驱动器121和第二栅极驱动器122。第一栅极驱动器121输出扫描信号scan(n-1)和scan(n),并且根据移位时钟将扫描信号scan1和scan2顺序地移位。第二栅极驱动器122输出em信号并且根据移位时钟将em信号顺序地移位。在没有边框的模型的情况下,构成第一栅极驱动器121和第二栅极驱动器122的开关元件中的至少一些可以被分布并设置在像素阵列中。

52.包括一个或更多个扫描信号和em信号的栅极信号可以被施加至像素电路。如图2所示,可以将两个扫描信号和一个em信号施加至像素电路。在图2中,像素线l1、l2和l3中的每个像素线连接至三条栅极线gl1、gl2和gl3。第一像素线l1通过栅极线gl1、gl2和gl3接收包括扫描信号scan0和scan1以及em信号em1的第一栅极信号g1。第二像素线l2通过栅极线gl1、gl2和gl3接收包括扫描信号scan1和scan2以及em信号em2的第二栅极信号g2。第n像素线l(n)通过栅极线gl1、gl2和gl3接收包括扫描信号scan(n-1)和scan(n)和em信号em(n)的第n栅极信号g(n)(其中n为正整数)。

53.定时控制器130从主机系统接收输入图像的像素数据和与像素数据同步的定时信号。定时信号包括垂直同步信号vsync、水平同步信号hsync、时钟信号clk和数据使能信号de。垂直同步信号vsync的一个时段是一个帧时段。水平同步信号hsync和数据使能信号de的一个时段是一个水平时段1h。数据使能信号de的脉冲与一个线数据同步,以被写入一条像素线的像素。由于可以通过对数据使能信号de进行计数的方法来知道帧时段和水平时段,因此可以省略垂直同步信号vsync和水平同步信号hsync。

54.主机系统可以是电视(tv)系统、机顶盒、导航系统、个人计算机(pc)、车辆系统、家庭影院系统、移动设备或可穿戴设备的主电路板。在移动设备和可穿戴设备中,定时控制器130、显示面板驱动器110、112和120以及电源150可以集成到一个驱动集成电路(ic)中。

55.定时控制器130可以在通过将输入帧频率乘以i(其中i是大于零的正整数)而获得的输入帧频率

×

i hz的帧频率上控制显示面板驱动器110、112和120的操作定时。在国家电

视标准委员会(national television standard committee,ntsc)标准中,输入帧频率为60hz,在逐行倒相制式(phase alternating line,pal)标准中,输入帧频率为50hz。定时控制器130可以将帧频率降低到1hz与30hz之间的频率,以便在低速驱动模式下降低像素的刷新率。

56.定时控制器130基于从主机系统接收的定时信号vsync、hsync和de产生用于控制数据驱动器110的操作定时的数据定时控制信号、用于控制解复用器112的操作定时的mux信号、以及用于控制栅极驱动器120的操作定时的栅极定时控制信号。从定时控制器130输出的栅极定时控制信号的电压电平可以通过在附图中省略的电平移位器被转换成栅极截止电压vgh和栅极导通电压vgl,使得栅极截止电压vgh和栅极导通电压vgl可以被提供至栅极驱动器120。电平移位器将栅极定时控制信号的低电平电压转换成栅极导通电压vgl,并将栅极定时控制信号的高电平电压转换成栅极截止电压vgh。

57.电源150可以包括电荷泵、调节器、降压转换器、升压转换器等。电源150通过调节来自主机系统的直流(dc)输入电压来产生驱动显示面板驱动器和显示面板100所需的电力。电源150可以输出诸如伽玛参考电压gma、栅极截止电压vgh、栅极导通电压vgl、像素驱动电压vdd、低电势电力电压vss、初始化电压vini和参考电压vref的直流电。伽马参考电压gma被提供至数据驱动器110。栅极截止电压vgh和栅极导通电压vgl被提供至栅极驱动器120。像素驱动电压vdd、低电位电力电压vss、初始化电压vini和参考电压vref通过图2中省略的电力线被共同提供至像素电路。像素驱动电压vdd被设置为高于低电位电力电压vss、初始化电压vini和参考电压vref的电压。

58.图3是示出本公开内容的像素电路的示意图。

59.参照图3,像素电路可以包括第一至第三电路单元10、20和30以及第一至第三连接部12、23和13。在像素电路中,可以省略或增加一个或更多个部件,并且可以包括内部补偿电路。

60.第一电路单元10将数据电压vdata提供至驱动元件dt。驱动元件dt可以被实现为包括栅极drg、源极drs和漏极drd的晶体管。第二电路单元20接收像素驱动电压vdd,对连接至驱动元件dt的栅极drg的电容器进行充电,并且在一个帧时段内保持电容器的电压。第三电路单元30将从驱动元件dt流过的电流提供至发光元件oled。发光元件oled将电流转换成光。第一连接部12连接第一电路单元10和第二电路单元20。第二连接部23连接第二电路单元20和第三电路单元30。第三连接部13连接第三电路单元30和第一电路单元10。

61.内部补偿电路可以包括第一至第三电路单元10、20和30。内部补偿电路对驱动元件dt的阈值电压vth进行采样,并且将补偿了多达阈值电压vth的电流提供至发光元件oled。

62.为了提高发光元件oled的效率,可以以串联结构来实现发光元件oled。图4示出了三堆叠串联结构的示例,但是应当注意,本公开内容不限于此。例如,双堆叠串联结构也是可能的。

63.参照图4,发光元件oled的有机化合物包括堆叠在阴极cat与阳极and之间的第一至第三堆叠部st1、st2和st3。第一堆叠部st1包括第一发光层eml1。第二堆叠部st2包括第二发光层eml2。第三堆叠部st3包括第三发光层eml3。有机化合物还包括设置在第一堆叠部st1与第二堆叠部st2之间的第一电荷产生层cgl1以及设置在第二堆叠部st2与第三堆叠部

st3之间的第二电荷产生层cgl2。

64.第一电荷产生层cgl1包括第一n型电荷产生层n-cgl1和第一p型电荷产生层p-cgl1。第一n型电荷产生层n-cgl1与第二电子传输层etl2接触,并且第一p型电荷产生层p-cgl1设置在第一n型电荷产生层n-cgl1与第一空穴传输层htl1之间。

65.第二电荷产生层cgl2包括第二n型电荷产生层n-cgl2和第二p型电荷产生层p-cgl2。第二n型电荷产生层n-cgl2与第三电子传输层etl3接触,并且第二p型电荷产生层p-cgl2设置在第二n型电荷产生层n-cgl2与第二空穴传输层htl2之间。

66.第一电荷产生层cgl1和第二电荷产生层cgl2中的每一个可以被设置为包括第一n型电荷产生层n-cgl1或第二n型电荷产生层n-cgl2的多个层,并且第一p型电荷产生层p-cgl1或第二p型电荷产生层p-cgl2可以设置为单层。

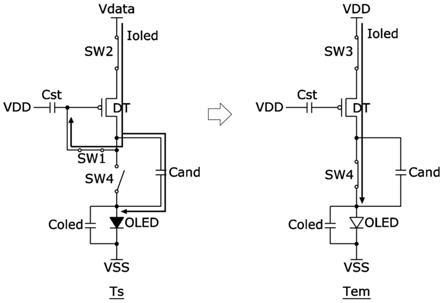

67.第一n型电荷产生层n-cgl1将电子注入到第二堆叠部st2中,并且第二n型电荷产生层n-cgl2将电子注入到第三堆叠部st3中。第一n型电荷产生层n-cgl1和第二n型电荷产生层n-cgl2中的每一个可以包括n型掺杂剂材料和n型主体材料。n型掺杂剂材料可以是选自元素周期表的第i族和第ii族的金属、可以注入电子的有机材料或它们的混合物中的一种。例如,n型掺杂剂材料可以是选自碱金属和碱土金属中的任何一种。第一n型电荷产生层n-cgl1和第二n型电荷产生层n-cgl2中的每一个可以形成为掺杂有碱金属例如锂(li)、钠(na)、钾(k)或铯(cs)或碱土金属例如镁(mg)、锶(sr)、钡(ba)或镭(ra)的有机层,但本公开内容不限于此。n型主体材料可以包括能够转移电子的材料,例如,选自三(8-羟基喹啉基)铝(alq3)(tris(8-hydroxyquinolino)aluminum(alq3))、8-羟基喹啉基锂(liq)(8-hydroxyquinolinolato-lithium(liq)、2-(4-联苯基)-5-(4-叔丁基苯基)-1,3,4-恶二唑(pbd)(2-(4-biphenylyl)-5-(4-tert-butylphenyl)-1,3,4-oxadiazole(pbd))、3-(4-联苯基)4-苯基-5-叔丁基苯基-1,2,4-三唑(taz)(3-(4-biphenyl)4-phenyl-5-tert-butylphenyl-1,2,4-triazole(taz))、螺-pbd(spiro-pbd)、双(2-甲基-8-喹啉酸酯)-4-(苯基苯酚基)铝(balq)(bis(2-methyl-8-quinolinolate)-4-(phenylphenolato)aluminum(balq))、salq、2,2,2-(1,3,5-苯甲三基)-三(1-苯基-1-h-苯并咪唑(tpbi)(2,2,2-(1,3,5-benzinetriyl)-tris(1-phenyl-1-h-benzimidazole)(tpbi))、恶二唑(oxadiazole)、三唑(triazole)、菲咯啉(phenanthroline)、苯并恶唑(benzoxazole)和苯并噻唑(benzthiazole)中的至少一种,但是本公开内容不限于此。

68.第一p型电荷产生层p-cgl1将空穴注入到第一堆叠部st1中,并且第二p型电荷产生层p-cgl2将空穴注入到第二堆叠部st2中。第一p型电荷产生层p-cgl1和第二p型电荷产生层p-cgl2中的每一个可以包括p型掺杂剂材料和p型主体材料。p型掺杂剂材料可以包括金属氧化物、有机材料例如四氟-四氰基喹二甲烷(f4-tcnq)(tetrafluoro-tetracyanoquinodimethane(f4-tcnq))、六氮杂苯并菲-六甲腈(hat-cn)(hexaazatriphenylene-hexacarbonitrile(hat-cn))或六氮杂苯并菲(hexaazatriphenylen)、或金属材料例如v2o5、moo

x

或wo3,但本公开内容不限于此。p型主体材料可以包括能够转移例如选自以下的至少一种的材料:(n,n'-双(萘-1-基)-n,n'-双(苯基)-2、2'-二甲基联苯胺(npd)((n,n'-bis(naphthalene-1-yl)-n,n'-bis(phenyl)-2,2'-dimethylbenzidine)(npd))、n,n'-双-(3-甲基苯基)-n(n,n

’‑

bis-(3-methylphenyl)-n),n'-双-(苯基)-联苯胺(tpd)(n

’‑

bis-(phenyl)-benzidine(tpd))和4,4',4-三(n-3-甲基

苯基-n-苯基-氨基)-三苯胺(mtdata)(4,4’,4-tris(n-3-methylphenyl-n-phenyl-amino)-triphenylamine(mtdata)),但是本公开内容不限于此。

69.第一堆叠部st1可以包括电子注入层eil、第一电子传输层etl1、第一发光层eml1、第一电子阻挡层ebl1和第一空穴传输层htl1。第二堆叠部st2可以包括第二电子传输层etl2、第二发光层eml2、第二电子阻挡层ebl2和第二空穴传输层htl2。第三堆叠部st3可以包括第三电子传输层etl3、第三发光层eml3、第三电子阻挡层ebl3、第三空穴传输层htl3和空穴注入层hil。

70.空穴注入层hil有助于从阳极and向第三发光层eml3注入空穴。空穴注入层hil可以包括例如选自双吡嗪并[2,3-f:2',3'-h]喹喔啉-2,3,6,7,10.11-六碳腈(hat-cn)(dipyrazino[2,3-f:2’,3

’‑

h]quinoxaline-2,3,6,7,10.11-hexacarbonitrile(hat-cn))、酞菁(cupc)、2,3,5,6-四氟-7,7,8,8-四氰基喹二甲烷(f4-tcnq)(2,3,5,6-tetrafluoro-7,7,8,8-tetracyanoquinodimethane(f4-tcnq))和n,n'-双(萘-1-基)-n,n'-双(苯基)-2,2'-二甲基联苯胺(npd)(n,n

’‑

bis(naphthalene-1-yl)-n,n

’‑

bis(phenyl)-2,2

’‑

dimethylbenzidine(npd))中的至少一种,但是本公开内容不限于此。

[0071]

第一至第三空穴传输层htl1、htl2和htl3分别平稳地将空穴传输至第一至第三发光层eml1、eml2和eml3。第一至第三空穴传输层htl1、htl2和htl3中的每一个可以包括例如选自npd、tpd、2,2',7,7'-四(n,n-二甲基氨基)-9,9-螺芴(s-tad)(2,2’,7,7

’‑

tetrakis(n,n-dimethylamino)-9,9-spirofluorene(s-tad))和mtdata中的至少一种,但是本公开内容不限于此。

[0072]

第一至第三电子阻挡层ebl1、ebl2和ebl3防止注入到第一至第三发光层eml1、eml2和eml3中的电子分别流向第一至第三空穴传输层htl1、htl2和htl3。第一至第三电子阻挡层ebl1、ebl2和ebl3阻挡电子的移动,以改善第一至第三发光层eml1、eml2和eml3中的空穴与电子之间的结合,并提高第一至第三发光层eml1、eml2和eml3的发光效率。第一至第三电子阻挡层ebl1、ebl2和ebl3中的每一个可以由与第一至第三空穴传输层htl1、htl2和htl3中的每一个的材料相同的材料制成,并且第一至第三空穴传输层htl1、htl2和htl3以及第一至第三电子阻挡层ebl1、ebl2和ebl3中的每一个可以形成为单独的层,但是本公开内容不限于此。例如,第一至第三空穴传输层htl1、htl2和htl3可以分别与第一至第三电子阻挡层ebl1、ebl2和ebl3集成。

[0073]

空穴和电子在第一至第三发光层eml1、eml2和eml3中复合以产生激子。第一至第三发光层eml1、eml2和eml3分别设置在第一至第三空穴传输层htl1、htl2和htl3与第一至第三电子传输层etl1、etl2和etl3之间,并且每个都包括能够发出特定颜色的光的材料。例如,第一发光层eml1可以包括能够发射绿光的材料,并且第二发光层eml2可以包括能够发射蓝光的材料。第三有机发光层eml3可以包括能够发射红光的材料。

[0074]

发光层eml1、eml2和eml3中的每个发光层可以包括主体-掺杂剂系统,即,少量发光掺杂剂材料被添加到占较大重量比的主体材料中。发光层eml1、eml2和eml3中的每个发光层可以包括多种主体材料或者可以包括单一主体材料。

[0075]

第一发光层eml1可以包括使主体材料掺杂的绿色磷光掺杂剂材料。第一发光层eml1可以是绿色发光层,并且从第一发光层eml1发射的光的波长可以在490nm至570nm的范围内。第一发光层eml1可以包括包含咔唑联苯(cbp)(carbazole biphenyl(cbp))或1,3-双

(咔唑-9-基(mcp)(1,3-bis(carbazol-9-yl(mcp))的主体材料,并且可以包括磷光材料,该磷光材料包括包含ir(ppy)3(fac三(2-苯基吡啶)铱)(ir(ppy)3(fac tris(2-phenylpyridine)iridium))、ir(ppy)2(acac)(ir(ppy)2(acac))或ir(mpyp)3(ir(mpyp)3)的掺杂剂材料,但是本公开内容不限于此。

[0076]

第二发光层eml2可以包括使主体材料掺杂的蓝色荧光掺杂剂材料。第二发光层eml2可以是蓝色发光层,并且从第二发光层eml2发射的光的波长可以在490nm至450nm的范围内。第二发光层eml2可以包括包含cbp或mcp的主体材料,并且可以包括荧光材料,该荧光材料包括选自螺-dpvbi、螺-6p、二苯乙烯基苯(dsb)(distyrylbenzene(dsb))、二苯乙烯基亚芳基(dsa)(distyrylarylene(dsa))、基于pfo的聚合物和基于ppv的聚合物,但是本公开内容不限于此。

[0077]

第三发光层eml3可以包括使主体材料掺杂的红色磷光掺杂剂材料。第三发光层eml3可以是红色发光层,并且从第三发光层eml3发射的光的波长可以在720nm至640nm的范围内。第三发光层eml3可以包括包含cbp或mcp的主体材料,并且可以包括磷光掺杂剂,该磷光掺杂剂包括选自piqir(acac)(双(1-苯基异喹啉)乙酰丙酮铱)(piqir(acac)(bis(1-phenylisoquinoline)acetylacetonate iridium))、pqir(acac)(双(1)-苯基喹啉)乙酰丙酮铱)(pqir(acac)(bis(1-phenylquinoline)acetylacetonate iridium))、btp2ir(acac)、pqir(三(1-苯基喹啉)铱)(pqir(tris(1-phenylquinoline)iridium))和ptoep(八乙基卟啉铂)(ptoep(octaethylporphyrin platinum))中的至少一种。

[0078]

第一至第三电子传输层etl1、etl2和etl3分别将来自电子注入层eil、第一n型电荷产生层n-cgl1和第二n型电荷产生层n-cgl2的电子转移到发光层eml。第一至第三电子传输层etl1、etl2和etl3可以用作空穴阻挡层(hbl)。hbl可以防止未参与发光层eml中的复合的空穴的泄漏。

[0079]

第一至第三电子传输层etl1、etl2和etl3可包括例如选自liq、pbd、taz、2,9-二甲基-4,7-二苯基-1(2,9-dimethyl-4,7-diphenyl-1)、10-菲咯啉(bcp)(10-phenanthroline(bcp))和balq中的至少一种,但是本公开内容不限于此。

[0080]

电子注入层eil促进电子注入到第一发光层eml1中。电子注入层eil可以包括例如选自碱金属或碱土金属离子形式例如lif、baf2和csf中的至少一种,但是本公开内容不限于此。

[0081]

由于具有串联结构的发光元件oled可以在低电流下发射具有高亮度的光,所以可以提高效率。由于发光元件oled的电容器coled的电容增加,所以电容器coled的充电时间可能在低电流下延迟。如图5所示,表现特性可能在低灰度下降低,并且在低速驱动模式下可能引起闪烁。图5是示出其中发光元件的亮度在低灰度(实线)下降低的示例的曲线图。在图5中,虚线表示理想的伽玛曲线。

[0082]

图6示出了说明根据本公开内容的第一实施方式的像素电路的电路图。图7示出了说明图6所示的像素电路的驱动方法的电路图。

[0083]

参照图6和图7,红色子像素包括第一驱动元件dt1、第一发光元件oled(r)、第一至第四开关元件sw1至sw4、连接至第一驱动元件dt1的栅电极的第一电容器cst1、连接在第一驱动元件dt1的第一电极与第一发光元件oled(r)的阳极and之间的第二电容器cand1、以及连接在第一发光元件oled(r)的阳极and与阴极cat阴极之间的第三电容器coled1。

[0084]

绿色子像素包括第二驱动元件dt2、第二发光元件oled(g)、第一至第四开关元件sw1至sw4、连接至第二驱动元件dt2的栅电极的第一电容器cst2、连接在第二驱动元件dt2的第一电极与第二发光元件oled(g)的阳极and之间的第二电容器cand2、以及连接在第二发光元件oled(g)的阳极and与阴极cat之间的第三电容器coled2。

[0085]

蓝色子像素包括第三驱动元件dt3、第三发光元件oled(b)、第一至第四开关元件sw1至sw4、连接至第三驱动元件dt3的栅电极的第一电容器cst3、连接在第三驱动元件dt3的第一电极与第三发光元件oled(b)的阳极and之间的第二电容器cand3、以及连接在第三发光元件oled(b)的阳极and与阴极cat之间的第三电容器coled3。

[0086]

在图6中,oled(r)表示红色子像素的发光元件,并且vdata(r)表示施加至红色子像素的数据电压。oled(g)表示绿色子像素的发光元件,并且vdata(g)表示施加至绿色子像素的数据电压。oled(b)表示蓝色子像素的发光元件,并且vdata(b)表示施加至蓝色子像素的数据电压。

[0087]

在图7中,图6中的oled(r)、oled(g)和oled(b)统一表示为oled,图6中的vdata(r)、vdata(g)和vdata(b)统一表示为vdata,图6中的dt1、dt2和dt3统一表示为dt,将图6中的cand1、cand2和cand3统一表示为cand,图6中的coled1、coled2和coled3统一表示为coled,以及图6中的cst1、cst2和cst3统一表示为cst。

[0088]

在子像素中的每个子像素中,第一开关元件sw1在第一步骤中导通以连接驱动元件dt1、dt2或dt3的栅电极和第二电极,然后在第二步骤中截止。如图7所示,可以根据第n扫描信号scan(n)的电压来导通或截止第一开关元件sw1。在以下描述的实施方式中,第一步骤可以包括采样步骤ts,第二步骤可以包括发光步骤tem。

[0089]

第二开关元件sw2在第一步骤中导通以将数据电压vdata(r)、vdata(g)或vdata(b)提供至驱动元件dt1、dt2或dt3的第一电极,然后在第二步骤中截止。如图7所示,第二开关元件sw2可以根据第n扫描信号scan(n)的电压而导通或截止。

[0090]

第三开关元件sw3在第一步骤中处于截止状态,并且在第二步骤中导通,以将像素驱动电压vdd提供至驱动元件dt1、dt2或dt3的第一电极。如图7所示,可以根据em信号em(n)的电压来导通或截止第三开关元件sw3。

[0091]

第四开关元件sw4在第一步骤中处于截止状态,并且在第二步骤中导通,以将驱动元件dt1、dt2或dt3的第二电极连接至发光元件oled(r)、oled(g)或oled(b)的阳极。如图7所示,可以根据em信号em(n)的电压来导通或截止第四开关元件sw4。

[0092]

在第一步骤中,根据流过驱动元件dt1、dt2和dt3的电流i对第二电容器cand1、cand2和cand3充电,以增加发光元件oled(r)、oled(g)和oled(b)的阳极电压。因此,在第一步骤中根据通过电容器耦合施加的电压对发光元件oled(r)、oled(g)和oled(b)的阳极和第三电容器coled1、coled2和coled3进行预充电。在第一步骤中,根据数据电压vdata(r)、vdata(g)和vdata(b)的灰度电压确定发光元件oled(r)、oled(g)和oled(b)的阳极和第三电容器coled1、coled2和coled3,并且因此发光元件oled(r)、oled(g)和oled(b)的阳极和第三电容器coled1、coled2和coled3根据像素数据的灰度值被设置为具有适当的电压。

[0093]

在第一步骤中,发光元件oled(r)、oled(g)和oled(b)根据流过驱动元件dt1、dt2和dt3的电流ioled发光。在这种情况下,即使当电流ioled低时,由于发光元件的电容器coled1、coled2和coled3被预充电,所以阳极电压迅速增加,从而提高了表现出低灰度的能

力。

[0094]

相对于第一电容器cst1、cst2或cst3的电容,第二电容器cand1、cand2或cand3的电容可以确定为在最大1:1与最小10:1之间的范围内。相对于第三电容器coled1、coled2或coled2的电容,第二电容器cand1、cand2或cand3的电容可以确定为在最大1:1与最小10:1之间的范围内。换句话说,第二电容器cand1的电容可以确定为在小于或等于第一电容器cst1的电容并且大于或等于第一电容器cst1的电容的1/10的范围内,第二电容器cand2的电容可以确定为在小于或等于第一电容器cst2的电容并且大于或等于第一电容器cst2的电容的1/10的范围内,以及第二电容器cand3的电容可以确定为在小于或等于第一电容器cst3的电容并且大于或等于第一电容器cst3的电容的1/10的范围内。另外,第二电容器cand1的电容可以确定为在小于或等于第三电容器coled1的电容并且大于或等于第三电容器coled1的电容的1/10的范围内,第二电容器cand2的电容可以确定为在小于或等于第三电容器coled2的电容并且大于或等于第三电容器coled2的电容的1/10的范围内,以及第二电容器cand3的电容可以确定为在小于或等于第三电容器coled3的电容并且大于或等于第三电容器coled3的电容的1/10的范围内。

[0095]

驱动元件dt1、dt2和dt3与发光元件oled(r)、oled(g)和oled(b)之间可能存在寄生电容,但是由于寄生电容小于1ff,因此第二电容器cand1、cand2或cand3的电容远大于寄生电容。

[0096]

第二电容器cand1、cand2和cand3可以以与存储电容器cst1、cst2和cst3相同的截面结构形成在显示面板100上。第二电容器cand1、cand2和cand3的电容可以根据子像素的颜色而不同地设置。例如,可以确定蓝色子像素的第二电容器cand3的电容的大小》红色子像素的第二电容器cand1的电容的大小》绿色子像素的的第二电容器cand2的电容的大小。

[0097]

根据子像素的颜色的第三电容器coled1、coled2和coled3的电容可以根据发光元件的有机化合物的厚度和开口率而变化。因此,电容器cand1、cand2和cand3的电容可以根据第三发光元件的电容器coled1、coled2和coled3来确定。

[0098]

图8是示出根据本公开内容的第二实施方式的像素电路的电路图。

[0099]

参照图8,像素电路包括发光元件oled、驱动元件dt、多个开关元件m1至m6、第一电容器cst、第二电容器cand等。驱动元件dt和开关元件m1至m6可以被实现为p沟道开关元件。

[0100]

像素驱动电压vdd通过vdd线(像素驱动电压线)pl1被提供至像素电路。低电位电力电压vss通过vss线pl2被提供至像素电路。初始化电压vini通过vini线(初始电压线)pl3被提供至像素电路。包括第(n-1)扫描信号scan(n-1)、第n扫描信号scan(n)和em信号em(n)的栅极信号被提供至像素电路。第(n-1)扫描信号scan(n-1)与第(n-1)像素线的数据电压vdata同步。第n扫描信号scan(n)与第n像素线的数据电压vdata同步。第n扫描信号scan(n)的脉冲产生为具有与第(n-1)扫描信号scan(n-1)相同的脉冲宽度,并且在第(n-1)扫描信号scan(n-1)的脉冲之后产生。

[0101]

驱动元件dt通过根据栅极-源极电压vgs控制在发光元件oled中流动的电流来驱动发光元件oled。驱动元件dt包括连接至第一节点n1的栅电极、连接至第二节点n2的第一电极、和连接至第三节点n3的第二电极。第一节点n1连接至第一电容器cst、驱动元件dt的栅电极和第一开关元件m1的第一电极。第二节点n2连接至第二开关元件m2的第一电极和第三开关元件m3的第二电极。第三节点n3连接至驱动元件dt的第二电极、第一开关元件m1的

第二电极和第四开关元件m4的第一电极。

[0102]

发光元件oled的阳极and连接至第四节点n4,并且其阴极cat连接至施加有低电位电力电压vss的vss线pl2。第四节点n4连接至发光元件oled的阳极and、第四开关元件m4的第二电极和第六开关元件m6的第二电极。发光元件oled包括形成在阳极and与阴极cat之间的第三电容器coled。

[0103]

第一电容器cst连接在vdd线pl1与第一节点n1之间。第二电容器cand连接在第三节点n3与第四节点n4之间。

[0104]

第一开关元件m1根据第n扫描信号scan(n)的栅极导通电压vgl而导通,以连接第一节点n1和第三节点n3。第一开关元件m1包括连接至第二栅极线gl2的栅电极、连接至第一节点n1的第一电极以及连接至第三节点n3的第二电极。第n扫描信号scan(n)通过第二栅极线gl2被提供至像素p。

[0105]

由于第一开关元件m1仅在一个帧时段的一个非常短的水平时段1h中导通(在该帧时段中,产生第n扫描信号scan(n)作为栅极导通电压vgl),因此第一开关元件m1在大约一帧时段内保持截止状态。因此,在第一开关元件m1的截止状态下可能产生泄漏电流。为了抑制第一开关元件m1的泄漏电流,如图12所示,第一开关元件m1可以被实现为具有其中两个晶体管串联连接的双栅极结构的晶体管。

[0106]

第二开关元件m2根据第n扫描信号scan(n)的栅极导通电压vgl而导通,以将数据线dl连接至第二节点n2。第二开关元件m2包括连接至第二栅极线gl2的栅电极、连接至第二节点n2的第一电极以及连接至数据线dl的第二电极。

[0107]

第三开关元件m3根据em信号em(n)的栅极导通电压vgl而导通,以将vdd线pl1连接至驱动元件dt的第一电极。第三开关元件m3包括连接至第三栅极线gl3的栅电极、连接至vdd线pl1的第一电极以及连接至第二节点n2的第二电极。em信号em(n)通过第三栅极线gl3被提供至像素电路。

[0108]

第四开关元件m4根据em信号em(n)的栅极导通电压vgl而导通,以将第三节点n3连接至第四节点n4。第四开关元件m4的栅电极连接至第三栅极线gl3。第四开关元件m4的第一电极连接至第三节点n3,并且第四开关元件m4的第二电极连接至第四节点n4。

[0109]

第五开关元件m5根据第(n-1)扫描信号scan(n-1)的栅极导通电压vgl而导通,以将第一节点n1连接至vini线pl3。第五开关元件m5包括连接至第一栅极线gl1的栅电极、连接至第一节点n1的第一电极以及连接至vini线pl3的第二电极。第(n-1)扫描信号scan(n-1)通过第一栅极线gl1被提供至像素电路。初始化电压vini通过vini线pl3被提供至像素电路。为了抑制第五开关元件m5的泄漏电流,如图12所示,第五开关元件m5可以被实现为具有其中两个晶体管串联连接的双栅极结构的晶体管。

[0110]

第六开关元件m6根据第n扫描信号scan(n)的栅极导通电压vgl而导通,以将vini线pl3连接至第四节点n4。第六开关元件m6包括连接至第二栅极线gl2的栅电极、连接至vini线pl3的第一电极以及连接至第四节点n4的第二电极。

[0111]

图9a至图11b是顺序示出图8所示的像素电路的操作的图。图9a是示出在初始化步骤ti中在像素电路中流动的电流的路径的电路图。图10a是示出在采样步骤ts中在像素电路中流动的电流的路径的电路图。图11a是示出在发光步骤tem中在像素电路中流动的电流的路径的电路图。图9b、图10b和图11b是示出施加至图8所示的像素电路的栅极信号的波形

图。在图9b、图10b和图11b中,箭头指示像素电路中的电流流动。

[0112]

参照图9a和图9b,在初始化步骤ti中,第(n-1)扫描信号scan(n-1)的电压是栅极导通电压vgl。在初始化步骤ti中,第n扫描信号scan(n)和em信号em(n)具有栅极截止电压vgh。在初始化步骤ti中,根据第(n-1)扫描信号scan(n-1)的栅极导通电压vgl,第五开关元件m5导通,以将第一节点n1放电至初始化电压vini。在这种情况下,第一节点n1被初始化。

[0113]

参照图10a和图10b,在采样步骤ts中,第n扫描信号scan(n)的电压是栅极导通电压vgl。在采样步骤ts中,第(n-1)扫描信号scan(n-1)和em信号em(n)具有栅极截止电压vgh。第一开关元件m1和第二开关元件m2在采样步骤ts中根据作为第n扫描信号scan(n)的电压的栅极导通电压vgl导通。在采样步骤ts中,通过经由第二电容器cand施加的电压对发光元件oled的阳极和第四节点n4进行预充电。在采样步骤ts中,将数据电压vdata施加至第二节点n2,并且将第一节点n1的电压改变为vdata+vth。“vth”表示驱动元件dt的阈值电压。因此,在采样步骤ts中,驱动元件dt的阈值电压vth被采样并且被充电在第一节点n1中。

[0114]

参照图11a和图11b,在发光步骤tem中的em信号em(n)的电压是栅极导通电压vgl。在发光步骤tem中,第(n-1)扫描信号scan(n-1)和第n扫描信号scan(n)具有栅极截止电压vgh。第三开关元件m3和第四开关元件m4在发光步骤tem中根据作为em信号em(n)的电压的栅极导通电压vgl导通。在发光步骤tem期间,电流可以通过驱动元件dt在发光元件oled中流动,使得发光元件oled可以发光。根据驱动元件dt的栅极-源极电压vgs来调节在发光元件oled中流动的电流。在发光步骤tem期间,驱动元件dt的栅极-源极电压vgs为vdata+vth-vdd。

[0115]

同时,如图13所示,可以在采样步骤ts与发光步骤tem之间设置保持步骤th。在保持步骤th中,像素电路的所有开关元件可以截止。

[0116]

图12是示出根据本公开内容的第三实施方式的像素电路的电路图。在图12中,将省略与上述实施方式相同的部件的详细描述。

[0117]

参照图12,像素电路包括发光元件oled、驱动元件dt、多个开关元件m1至m9、第一电容器cst、第二电容器cand等。驱动元件dt和开关元件m1至m9可以被实现为p沟道开关元件。

[0118]

初始化电压vini可以分为用于初始化驱动元件dt的第一初始化电压vini1和用于初始化发光元件oled的第二初始化电压vini2。第一初始化电压vini1和第二初始化电压vini2可以被设置为相同或不同的电压。初始化电压vini1通过vini线pl31被提供至像素电路,以及初始化电压vini2通过vini线pl32被提供至像素电路。

[0119]

驱动元件dt通过根据栅极-源极电压vgs控制在发光元件oled中流动的电流来驱动发光元件oled。驱动元件dt包括连接至第一节点n1的栅电极、连接至第二节点n2的第一电极和连接至第三节点n3的第二电极。

[0120]

发光元件oled的阳极and连接至第四节点n4,并且其阴极cat连接至施加有低电位电力电压vss的vss线pl2。发光元件oled包括形成在阳极and与阴极cat之间的第三电容器coled。

[0121]

第一电容器cst连接在vdd线pl1与第一节点n1之间。第二电容器cand连接在第三节点n3与第四节点n4之间。

[0122]

第一开关元件m1根据第n扫描信号scan(n)的栅极导通电压vgl而导通,以连接第

一节点n1和第三节点n3。第n扫描信号scan(n)通过第二栅极线gl2被提供至像素p。为了抑制第一开关元件m1的泄漏电流,第一开关元件m1可以被实现为具有其中两个晶体管串联连接的双栅极结构的晶体管。

[0123]

第二开关元件m2根据第n扫描信号scan(n)的栅极导通电压vgl而导通,以将数据线dl连接至第二节点n2。第三开关元件m3根据em信号em(n)的栅极导通电压vgl而导通,以将vdd线pl1连接至驱动元件dt的第一电极。em信号em(n)通过第三栅极线gl3被提供至像素电路。第四开关元件m4根据em信号em(n)的栅极导通电压vgl而导通,以将第三节点n3连接至第四节点n4。

[0124]

第五开关元件m5根据第(n-1)扫描信号scan(n-1)的栅极导通电压vgl而导通,以将第一节点n1连接至vini线pl3。第五开关元件m5包括连接至第一栅极线gl1的栅电极、连接至第一节点n1的第一电极以及连接至vini线pl3的第二电极。第(n-1)扫描信号scan(n-1)通过第一栅极线gl1被提供至像素电路。为了抑制第五开关元件m5的泄漏电流,第五开关元件m5可以被实现为具有其中两个晶体管串联连接的双栅极结构的晶体管。

[0125]

第六开关元件m6根据第n扫描信号scan(n)的栅极导通电压vgl而导通,以将第二vini线pl32连接至第四节点n4。第六开关元件m6包括连接至第二栅极线gl2的栅电极、连接至第二vini线pl32的第一电极以及连接至第四节点n4的第二电极。

[0126]

第七开关元件m7根据em信号em(n)的栅极导通电压vgl而导通,以将vdd线pl1连接至第五节点n5。第七开关元件m7的栅电极连接至施加有em信号em(n)的第三栅极线gl3。第七开关元件m7的第一电极连接至vdd线pl1,并且其第二电极连接至第五节点n5。第五节点n5连接至第一电容器cst、第七开关元件m7的第二电极、第八开关元件m8的第二电极、和第九开关元件m9的第二电极。在发光步骤tem中第七开关元件m7导通以将像素驱动电压vdd施加至第一节点n1,使得驱动元件dt的栅极-源极电压被设置为vref-vdata。因此,在本公开内容中,在使用第七开关元件m7的发光步骤tem中通过驱动元件dt在发光元件oled中流动的电流不受vdd的影响,从而防止了由于vdd的ir降引起的亮度偏差。

[0127]

第八开关元件m8在初始化步骤ti中根据第(n-1)扫描信号scan(n-1)的栅极导通电压vgl而导通,以将被施加参考电压vref的vref线(参考电压线)pl4连接至第五节点n5。第八开关元件m8的栅电极连接至施加有第(n-1)扫描信号scan(n-1)的第一栅极线gl1。第八开关元件m8的第一电极连接至vref线pl4,并且其第二电极连接至第五节点n5。

[0128]

第九开关元件m9在采样步骤ts中根据第n扫描信号scan(n)的栅极导通电压vgl而导通,以将被施加参考电压vref的vref线pl4连接至第五节点n5。第九开关元件m9的栅电极连接至被施加第n扫描信号scan(n)的第二栅极线gl2。第九开关元件m9的第一电极连接至vref线pl4,并且其第二电极连接至第五节点n5。

[0129]

第八开关元件m8和第九开关元件m9在初始化步骤ti和采样步骤ts中保持第五节点n5的电压作为参考电压vref。

[0130]

像素电路通过在子像素中的每个子像素中对驱动元件dt的阈值电压vth进行实时采样来补偿数据电压vdata达与阈值电压vth一样多。在像素电路的情况下,由于参考电压vref被施加至第一电容器cst,所以即使在制造过程中电容器cst短路时,也不会引起暗点缺陷,因此不会对图像质量产生明显的不利影响。特别地,在图3所示的像素电路中,可以将数据线dl的电压直接施加至驱动元件dt以对驱动元件dt的阈值电压vth进行采样,并且根

据屏幕位置像素驱动电压vdd的ir降可以被补偿以改善亮度偏差。

[0131]

图13是示出图12所示的像素电路的驱动方法的波形图。在图13中,dtg表示驱动元件dt的栅极电压,并且dts表示驱动元件dt的第一电极(或源电极)的电压。

[0132]

参照图13,在初始化步骤ti中,产生第(n-1)扫描信号scan(n-1)作为栅极导通电压vgl的脉冲。在这种情况下,第n扫描信号scan(n)和第n em信号em(n)保持栅极截止电压vgh。因此,在初始化步骤ti中,第五和第八开关元件m5和m8导通,并且其余的开关元件m1至m4、m6、m7和m9保持截止状态。

[0133]

第(n-1)像素线的采样步骤ts和第(n-1)像素线的初始化步骤ti通过第(n-1)扫描信号scan(n-1)同时产生。第(n-1)扫描信号scan(n-1)与要写入第(n-1)像素线的子像素的数据电压vdata同步,以将数据电压vdata提供至设置在第(n-1)像素线上的子像素的第一节点n1。同时,第(n-1)扫描信号scan(n-1)将像素驱动电压vdd提供至第n像素线的子像素中的第五节点n5。

[0134]

在初始化步骤ti中,第二节点n2的电压即驱动元件dt的第一电极电压处于浮置状态,这是因为第二开关元件m2和第三开关元件m3处于截止状态。第一节点n1的电压被初始化为第一初始化电压vini1,这是因为在初始化步骤ti中第五开关元件m5被导通。第五节点n5的电压是像素驱动电压vdd,这是因为在初始化步骤ti中第八开关元件m8被导通。

[0135]

在采样步骤ts中,将第n扫描信号scan(n)生成为栅极导通电压vgl的脉冲,并且将要写入第n像素线的子像素的数据电压vdata从数据驱动器110输出。在这种情况下,第(n-1)扫描信号scan(n-1)被反相为栅极截止电压vgh,并且第n信号em(n)保持栅极截止电压vgh。因此,在采样步骤ts中,第一开关元件m1、第二开关元件m2、第六开关元件m6和第九开关元件m9导通,并且其余的开关元件m3、m4、m5和m7和m8保持截止状态。

[0136]

在第n像素线的采样步骤ts中,要写入第n像素线的子像素的数据电压vdata被与第n扫描信号scan(n)的脉冲同步,从而被提供至设置在第n像素线上的子像素的第二节点n2。

[0137]

在采样步骤ts中,第一开关元件m1导通以连接驱动元件dt的栅电极和第二电极。在采样步骤t中,由于第一节点n1和第三节点n3通过第一开关元件m1连接,所以当第三节点n3的电压通过驱动元件dt增加到数据电压vdata时,第一节点n1的电压增加。在采样步骤ts中,当驱动元件dt的栅极电压dtg增加以达到驱动元件dt的阈值电压vth的绝对值(|vth|)时,驱动元件dt导通。因此,在采样步骤ts和保持步骤th中,将vref-(vdata-|vth|)存储在第一电容器cst中,从而对驱动元件dt的阈值电压vth进行采样。第一开关元件m1应该在发光步骤tem中被截止以保持截止状态,使得流过驱动元件dt的电流流到发光元件oled。

[0138]

在采样步骤ts中,第二节点n2的电压dts为数据电压vdata,这是因为第二开关元件m2导通并且第三开关元件m3处于截止状态。在采样步骤ts中,第二节点n2的电压即驱动元件dt的栅极电压dtg从vref-vdd+vini1变为vdata-|vth|。在采样步骤ts中,由于参考电压vref通过第八开关元件m8施加,所以第五节点n5的电压从vdd降低到vref。在采样步骤ts中,当第五开关元件m5截止时,通过电容器耦合,第一节点n1的电压下降多达其中第五节点n5的电压从vdd降低至vref的程度,从而降低到vref

–

vdd+vini1,然后变成vdata-|vth|。

[0139]

在保持步骤th中,栅极信号scan(n-1)、scan(n)和em(n)保持栅极截止电压vgh,使得所有开关元件m1至m9保持截止状态。因此,像素电路的主节点n1至n5浮置以保持驱动元

件dt的阈值电压感测操作。

[0140]

在发光步骤tem中,第n em信号em(n)被反相为栅极导通电压vgl。在这种情况下,扫描信号scan(n-1)和scan(n)保持栅极截止电压vgh。因此,在发光步骤tem中,第三开关元件m3、第四开关元件m4和第七开关元件m7导通,并且其余的开关元件m1、m2、m5、m8和m9保持截止状态。

[0141]

在发光步骤tem中,第一节点n1和第五节点n5的电压由于通过第三开关元件m2和第九开关元件m9提供的像素驱动电压vdd而变为vdd。在发光步骤tem中,第二节点n1的电压即驱动元件dt的栅极电压dtg变为vdd-vref+vdata-|vth|。在发光步骤tem中,如下面的等式所示,由于发光元件oled的电流ioled不受驱动元件dt的阈值电压vth的影响,所以该电流ioled补偿了驱动元件dt的周期变化或者像素之间的阈值电压vth的偏差,并且不受像素驱动电压vdd的ir下降引起的像素驱动电压vdd的变化的影响。

[0142][0143]

在此,k是指由驱动元件dt的电荷迁移率、寄生电容以及沟道电容确定的比例常数。vgs是指驱动元件dt的栅极-源极电压。

[0144]

在本公开内容中,通过在驱动元件与发光元件的阳极之间添加电容器,可以在采样步骤中利用电容器耦合效应来使低灰度电压的充电延迟最小化。因此,在本公开内容中,不需要单独的光学补偿算法来改善低灰度表现特性,可以改善低灰度表现特性,并且可以减少低速驱动模式下的闪烁。

[0145]

此外,在本公开内容中,当数据电压具有大的波动范围时,例如,当数据电压从黑色灰度电压变为白色灰度电压时,可以使响应延迟最小化以改善响应特性。

[0146]

本公开内容的效果不限于上述效果,并且本领域技术人员从权利要求的描述中可以清楚地理解其他效果。

[0147]

本公开可以包括以下构成。

[0148]

方案1.一种像素电路,包括:

[0149]

发光元件,其包括阳极与阴极;

[0150]

驱动元件,其包括连接至第一节点的栅电极、连接至第二节点的第一电极、以及连接至第三节点并将电流提供至所述发光元件的第二电极;

[0151]

第一开关元件,其被配置成在采样步骤中将所述第一节点连接至所述第三节点;

[0152]

第二开关元件,其被配置成在所述采样步骤中将数据电压提供至所述第二节点;

[0153]

第三开关元件,其被配置成在所述采样步骤之后的发光步骤中将像素驱动电压提供至所述第二节点;

[0154]

第四开关元件,其被配置成在所述发光步骤中将所述第三节点连接至所述发光元件的所述阳极;

[0155]

第一电容器,其连接至所述第一节点;

[0156]

第二电容器,其连接在所述第三节点与所述发光元件的所述阳极之间;以及

[0157]

第三电容器,其连接在所述发光元件的所述阳极与所述阴极之间。

[0158]

方案2.根据方案1所述的像素电路,其中,所述第二电容器与所述第一电容器或所述第三电容器的电容比小于或等于1:1。

[0159]

方案3.根据方案2所述的像素电路,其中,所述第二电容器的电容大于或等于所述第一电容器或所述第三电容器的电容的1/10。

[0160]

方案4.根据方案1所述的像素电路,其中,在包括所述像素电路的红色子像素、绿色子像素和蓝色子像素中,所述第二电容器具有不同的电容。

[0161]

方案5.根据方案4所述的像素电路,其中,所述蓝色子像素中的所述第二电容器的电容》所述红色子像素中的所述第二电容器的电容》所述绿色子像素中的所述第二电容器的电容。

[0162]

方案6.根据方案1所述的像素电路,其中,所述第二电容器的电容大于所述驱动元件与所述发光元件之间的寄生电容。

[0163]

方案7.根据方案1所述的像素电路,其中,所述第一开关元件和所述第二开关元件在所述采样步骤中响应于生成为栅极导通电压的脉冲的第n扫描信号同时导通,其中,n是大于或等于1的正整数;以及

[0164]

所述第三开关元件和所述第四开关元件在从所述采样步骤之前的初始化步骤到所述发光步骤开始,根据生成为栅极截止电压的脉冲的发光em信号保持截止状态,并且在所述em信号变成所述栅极导通电压的所述发光步骤中导通。

[0165]

方案8.根据方案7所述的像素电路,还包括:

[0166]

第五开关元件,其在所述初始化步骤中根据生成为所述栅极导通电压的脉冲的第n-1扫描信号而导通,以将所述第一节点连接至施加有初始化电压的初始化电压线;和

[0167]

第六开关元件,其在所述采样步骤中根据所述第n扫描信号的所述栅极导通电压而导通,以将所述初始化电压线连接至与所述发光元件的所述阳极连接的第四节点。

[0168]

方案9.根据方案8所述的像素电路,其中,所述初始化电压包括用于初始化所述驱动元件的第一初始化电压和用于初始化所述发光元件的第二初始化电压,

[0169]

所述第五开关元件根据所述第n-1扫描信号的所述栅极导通电压而导通,以将所述第一节点连接至施加有所述第一初始化电压的第一初始化电压线,以及

[0170]

所述第六开关元件根据所述第n扫描信号的所述栅极导通电压而导通,以将施加有所述第二初始化电压的第二初始化电压线连接至所述第四节点。

[0171]

方案10.根据方案9所述的像素电路,还包括:第七开关元件,其在所述发光步骤中根据所述em信号的所述栅极导通电压而导通,以将施加有所述像素驱动电压的像素驱动电压线连接至与所述第一电容器连接的第五节点。

[0172]

方案11.根据方案10所述的像素电路,还包括:

[0173]

第八开关元件,其在所述初始化步骤中根据所述第n-1扫描信号的所述栅极导通电压而导通,以将施加有参考电压的参考电压线连接至所述第五节点;和

[0174]

第九开关元件,其在所述采样步骤中根据第n扫描信号的所述栅极导通电压而导通,以将所述参考电压线连接至所述第五节点。

[0175]

方案12.一种显示装置,包括:

[0176]

数据驱动器,其被配置成将数据电压提供至数据线;

[0177]

栅极驱动器,其被配置成在初始化步骤中将生成为栅极导通电压的脉冲的第n-1扫描信号提供至第一栅极线,在所述初始化步骤之后的采样步骤中将生成为所述栅极导通电压的所述脉冲的第n扫描信号提供至第二栅极线,以及在所述采样步骤之后的发光步骤中将生成为所述栅极导通电压的发光信号提供至第三栅极线,其中,n是大于或等于1的正整数;

[0178]

电源,其被配置成输出像素驱动电压以及低于所述像素驱动电压的低电位电力电压和初始化电压;以及

[0179]

包括连接至所述数据线和所述第一栅极线至所述第三栅极线的像素电路的红色子像素、绿色子像素和蓝色子像素,

[0180]

其中,所述像素电路包括:

[0181]

发光元件,其包括阳极与阴极。

[0182]

驱动元件,其包括连接至第一节点的栅电极、连接至第二节点的第一电极、以及连接至第三节点并将电流提供至所述发光元件的第二电极;

[0183]

第一开关元件,其被配置成在所述采样步骤中将所述第一节点连接至所述第三节点;

[0184]

第二开关元件,其被配置成在所述采样步骤中将所述数据电压提供至所述第二节点;

[0185]

第三开关元件,其被配置成在所述采样步骤之后的发光步骤中将所述像素驱动电压提供至所述第二节点;

[0186]

第四开关元件,其被配置成在所述发光步骤中将所述第三节点连接至所述发光元件的所述阳极;

[0187]

第一电容器,其连接至所述第一节点;

[0188]

第二电容器,其连接在所述第三节点与所述发光元件的所述阳极之间;以及

[0189]

第三电容器,其连接在所述发光元件的所述阳极与所述阴极之间。

[0190]

方案13.根据方案12所述的显示装置,其中,在所述红色子像素、所述绿色子像素和所述蓝色子像素中,所述第二电容器具有不同的电容。

[0191]

方案14.根据方案13所述的显示装置,其中,所述蓝色子像素中的所述第二电容器的电容》所述红色子像素中的所述第二电容器的电容》所述绿色子像素中的所述第二电容器的电容。

[0192]

方案15.一种包括上述像素电路的显示装置。

[0193]

上述本公开内容要实现的目的、用于实现本发明目的的手段以及本公开内容的效果并未指定权利要求的基本特征,因此,权利要求的范围不限于本发明的公开范围。

[0194]

尽管已经参考附图更详细地描述了本公开内容的实施方式,但是本公开内容不限于此,并且可以以许多不同的形式来实施而不背离本公开内容的技术构思。因此,提供本公开内容中公开的实施方式仅出于说明的目的,并不旨在限制本公开内容的技术构思。本公开内容的技术构思的范围不限于此。因此,应当理解,上述实施方式在所有方面都是示例性的,并且不限制本公开内容。本公开内容的保护范围应基于所附权利要求来解释,并且在其

等同范围内的所有技术构思应被解释为落入本公开内容的范围内。